Using Components

Begin with the design of bottom units in VHDL

Save each unit in a separate VHDL file

Design the top unit next, placing bottom units as components

Name the project as the top unit and then compile

Example:

Using half adder as a component in the full adder

First design the half adder in file half_adder.vhd

Compile and simulate the design to make sure it works

properly.

=========Half Adder=========================

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY half_adder IS

PORT (A, B : IN std_logic;

Sum, Cout : OUT std_logic);

END half_adder;

ARCHITECTURE myadd OF half_adder IS

BEGIN

Sum <= A xor B;

Cout <= A and B;

END myadd;

===========================================

Next, define a new file fulladder.vhd in the same directory

where half_adder.vhd resides. Use half adder as a component

in the full adder

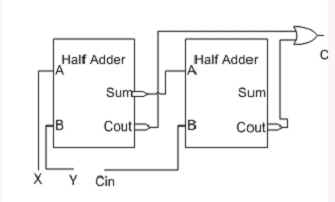

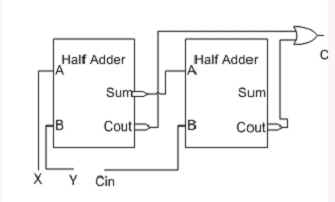

First Let us draw the diagram in order to determine the requirements of the design

This circuit uses two instances of the component half adder. It also uses an OR gate which gets its inputs from internal lines. VHDL calls the internal lines as signals and the boxes shown as components. Now look the source code:

=============Full Adder=========================

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY full_adder IS

PORT (A1, B1, Cin1 : IN std_logic;

Sum, Co1 : OUT std_logic);

END full_adder;

ARCHITECTURE myfulladd OF full_adder IS

signal Sum1,Cout1,Cout2:std_logic;

Component half_adder

port (A,B:in std_logic;

Sum, Cout:out std_logic);

end component;

BEGIN

H1:half_adder port map(A1,Cin1,Sum1,Cout1);

H2:half_adder port map(Sum1,B1,Sum,Cout2);

Co1 <= Cout1 or Cout2;

END myfulladd;

======================================================